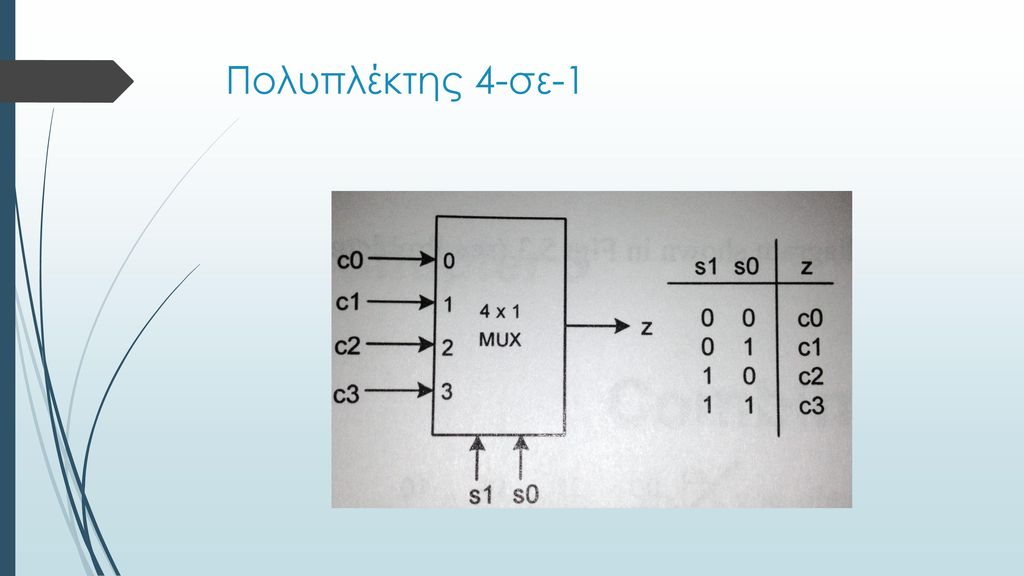

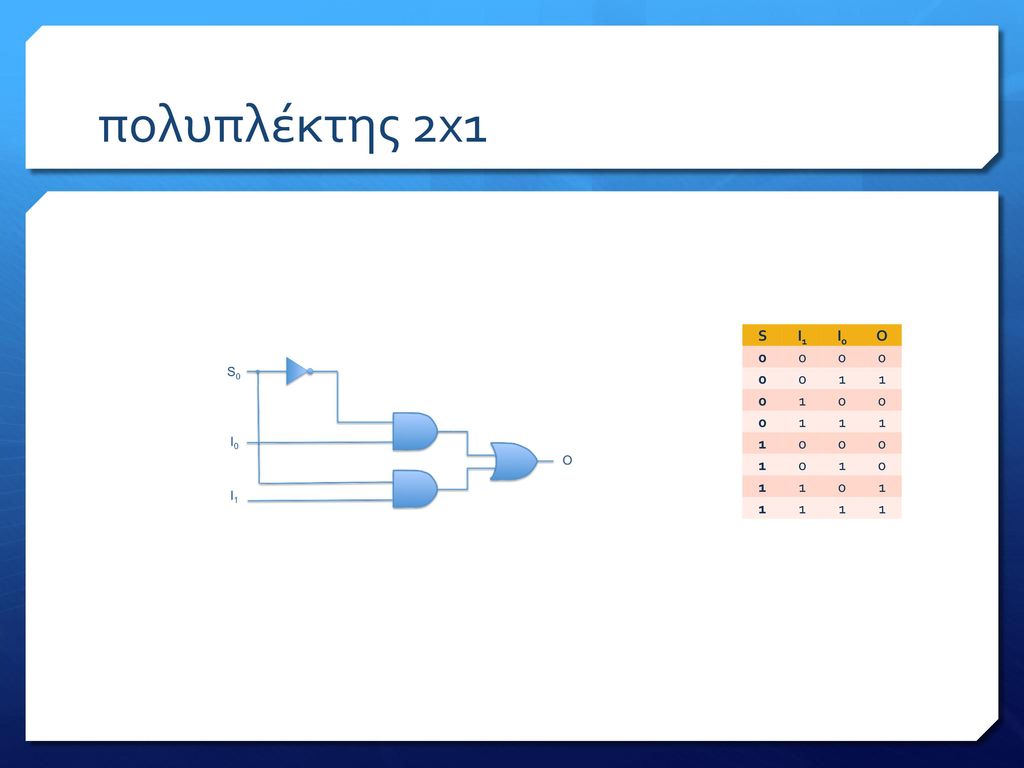

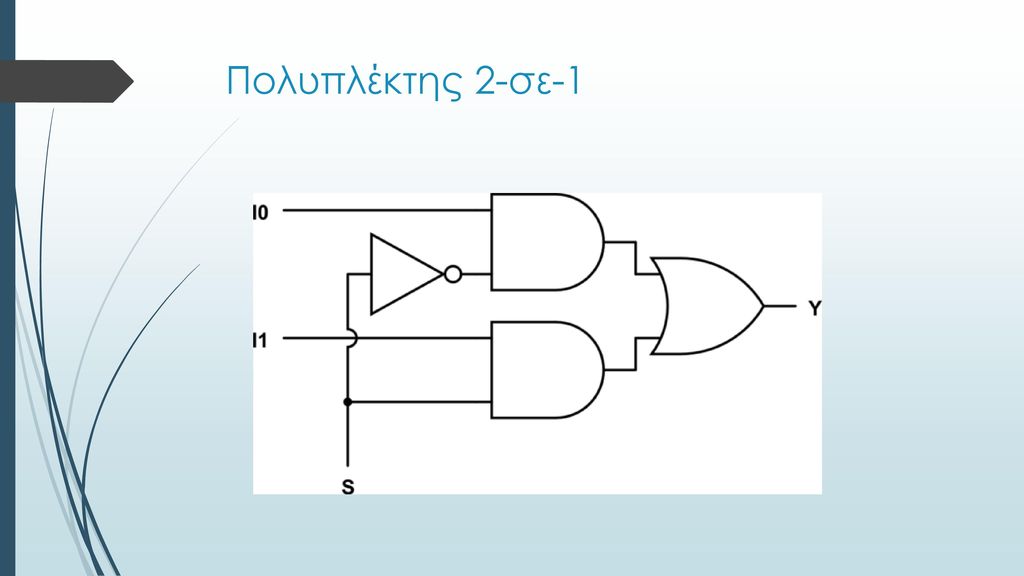

Αναφορά project στο μάθημα επιλογής "Εισαγωγή σε VLSI" ©2007 ΔΙΑΜΑΝΤΟΠΟΥΛΟΣ ΔΙΟΝΥΣΗΣ Α.Μ.2841 - ΑΓΓΕΛΟΠΟΥΛΟΣ ΓΙΩΡΓΟΣ Α.Μ.3020 Εισαγωγή Πύλες Πολυπλέκτης D - FLIP FLOP alu Υπο-κατηγορίες Πύλες +--------> NAND 2-3 +--------> NOR ...

Αναφορά project στο μάθημα επιλογής "Εισαγωγή σε VLSI" ©2007 ΔΙΑΜΑΝΤΟΠΟΥΛΟΣ ΔΙΟΝΥΣΗΣ Α.Μ.2841 - ΑΓΓΕΛΟΠΟΥΛΟΣ ΓΙΩΡΓΟΣ Α.Μ.3020 Εισαγωγή Πύλες Πολυπλέκτης D - FLIP FLOP alu Υπο-κατηγορίες Πύλες +--------> NAND 2-3 +--------> NOR ...